# **Microprocessor Products**

**Objective Data**

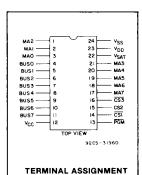

CDP18U42CD

# 256-Word x 8-Bit Static **EPROM** (Erasable/ Programmable Read-Only Memory)

#### Features:

- Static silicon-gate CMOS circuitry—

- CD4000-series compatible

- Compatible with CDP1800-series microprocessors

- Single voltage supply (during READ): 4-6.5 V

- Low power dissipation (READ): 20 mW

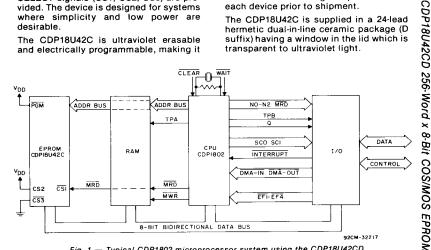

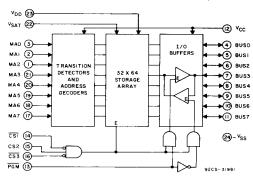

The RCA-CDP18U42C is a static CMOS, 2048-bit programmable read-only memory, organized as 256 words by 8 bits. It is compatible with the CDP1802 microprocessor and will interface directly with the CDP1802 as shown in the system diagram (Fig. 1). The CDP18U42C has common data inputs and data outputs and utilizes a single power supply during read operations. RCA ion implanted, silicon-gate, CMOS technology is employed in the CDP18U42C. Three CHIP-SELECT signals (CS1, CS2, CS3) are provided. The device is designed for systems where simplicity and low power are desirable.

The CDP18U42C is ultraviolet erasable and electrically programmable, making it

- Fast access time: 1 µs max.

- Fast programming time: 5 sec. typ.

- Data retention (125°C): 17.3 years typ.

- Write/erase endurance > 300 cycles

- 3-state outputs, TTL compatible

- Functional replacement for 1700-series UV erasable PROMs

ideally suited for experimentation and other uses where rapid design changes are necessary. Complete programming and functional testing are performed on each device prior to shipment.

The CDP18U42C is supplied in a 24-lead hermetic dual-in-line ceramic package (D suffix) having a window in the lid which is transparent to ultraviolet light.

Fig. 1 — Typical CDP1802 microprocessor system using the CDP18U42CD.

Information on these devices is intended for engineering evaluation. The type designations and data are subject to change, unless otherwise arranged. No obligations are assumed for notice of change or future manufacture of these devices.

Information furnished by RCA is believed to be accurate and reliable. However, no responsibility is assumed by RCA for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of RCA.

Printed in USA/11-79

Trademark(s)® Registered Marca(s) Registrada(s)

# **Erasing Procedure**

The CDP18U42CD may be erased when exposed to high-intensity short-wave ultraviolet light at a wavelength of 2537 Angstroms. An example of an ultraviolet light source which will erase a CDP18U42CD in 5 to 20 minutes is the Ultra Violet Products Model S-52T lamp, which should be used without short-wave filters and with the PROM placed within 1 inch of the lamp tubes.

The erase procedure is a bulk erase in which all 2048 bits (256 x 8) assume a 0 state (OUTPUTS = LOW), allowing the user to program a new bit pattern.

The erase characteristics of the CDP18U42CD are such that erasure begins to occur when exposed to light with wavelengths shorter than approximately 4000 Angstroms. It should be noted that light from the sun and from certain types of fluorescent lamps contains wavelengths in the 3000-4000 Angstrom range. Extended exposure of the CDP18U42CD to these types of lighting conditions will require opaque labels to be placed over the transparent lid to prevent unintentional erasure.

#### **Programming Procedure**

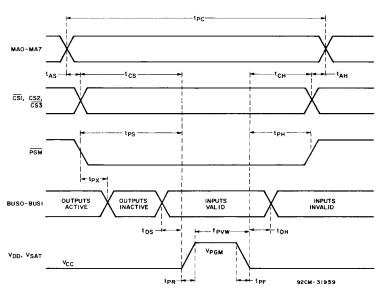

After being erased, the CDP18U42C exhibits a zero state (OUTPUT = LOW) in all locations. Programming is accomplished by introducing a 1 state (OUTPUT = HIGH) in the desired bit locations. Programming is done on a byte basis, in which any previously erased bits may be selectively programmed to a 1 state. This feature allows the user to change any 0 bits to 1's within a particular byte in an already programmed CDP18U42C without having to do a bulk program or a bulk erase. The program procedure consists of adthe dressing a word, selecting CDP18U42C, with the PGM (PROGRAM) input at a logic 0 (VSS), and raising the VDD and VSAT inputs to the proper program voltage (22 V typ.). The data to be programmed is applied to the BUS0-BUS7 inputs. See Fig. 3.

#### Read Procedure

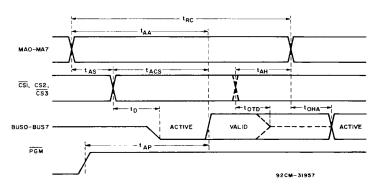

During a read operation, the CDP18U42C functions as a normal CMOS ROM. The read procedure consists of addressing a word and selecting the CDP18U42C, with the PGM input at a logic 1 (VDD.VSAT = VCC). Data is read at the BUSO-BUS7 outputs. See Fig. 4.

Fig. 2 - Block diagram for CDP18U42CD.

# MAXIMUM RATINGS, Absolute-Maximum Values:

| DC SUPPLY-VOLTAGE RANGE                                              |

|----------------------------------------------------------------------|

| (All voltage values referenced to VSS terminal)                      |

| V <sub>CC</sub> (READ, PROGRAM)                                      |

| V <sub>DD</sub> (READ)                                               |

| V <sub>DD</sub> (PROGRAM)                                            |

| V <sub>SAT</sub> (READ)                                              |

| V <sub>SAT</sub> (PROGRAM)                                           |

| INPUT VOLTAGE RANGE, ALL INPUTS – 0.5 to V <sub>CC</sub> + 0.5 V     |

| DC INPUT CURRENT, ANY ONE INPUT                                      |

| OPERATING-TEMPERATURE RANGE (TA) 40 to +85 °C                        |

| STORAGE-TEMPERATURE RANGE (T <sub>stg</sub> )                        |

| LEAD TEMPERATURE (DURING SOLDERING):                                 |

| At distance 1/16 ± 1/32 inch (1.59 ± 0.79 mm) from case for 10 s max |

STATIC ELECTRICAL CHARACTERISTICS at T<sub>A</sub> = -40 to +85 °C, unless otherwise noted.

|                     |          | CO         | NDITIO | NS      | LIMITS |      |          |          |      |            |

|---------------------|----------|------------|--------|---------|--------|------|----------|----------|------|------------|

| CHARACTERISTIC      |          | Vo         | VIN    | VCC     | VDD    | VSAT | CD       | P18U42   | 2CD  | UNITS      |

|                     |          | (V)        | (V)    | (V)     | (V)    | (V)  | Min.     | Тур.*    | Max. | _          |

| Quiescent Device    |          |            |        |         |        |      |          |          |      |            |

| Current:            |          |            | ľ      |         | 1      |      |          |          |      |            |

| Read Operation      |          |            |        |         | ļ      |      |          |          |      | 1          |

| lcc                 |          | L          | 0,5    | 5       | 5      | 5    | _        | 10       | 100  |            |

| IDD                 |          |            | 0,5    | 5       | 5      | 5    | _        | 10       | 100  |            |

| ISAT                |          | _          | 0,5    | 5       | 5      | 5    | _        | 1        | 10   |            |

| Program Operation   |          |            |        |         |        |      |          |          |      | μA         |

| lcc                 |          |            | 0,5    | 5       | 22     | 22   | -        | 10       | 100  | ]          |

| IDD                 |          |            | 0,5    | 5       | 22     | 22   |          | 10       | 100  | ]          |

| SAT                 |          |            | 0,5    | 5       | 22     | 22   | _        | 1        | 10   |            |

| Output Low Drive    |          |            |        |         |        |      |          |          |      |            |

| (Sink Current)      | lol      | 0.4        | 0,5    | 5       | —      | _    | 1.6      | 2        | —    | mA         |

| Output High Drive   |          |            |        |         |        |      |          |          |      | ''''^      |

| (Source Current)    | ЮН       | 4.6        | 0,5    | 5       | _      |      | - 1.6    | - 2      | l —  | Į.         |

| Output Voltage      |          |            |        |         |        |      |          |          | T -  |            |

| (Low Level)         | VOL      | _ '        | 0,5    | 5       | _      | _    | _        | 0        | 0.05 | l v        |

| Output Voltage      |          |            |        |         |        |      |          |          |      | 1 °        |

| (High Level)        | Vон      | -          | 0,5    | 5       | l —    | -    | 4.95     | 5        | l —  |            |

| Input Voltage       |          |            |        |         |        |      |          |          |      |            |

| (Low Level)         | $v_{IH}$ | 0.5,4.5    | -      | 5       | _      |      | <u> </u> | . –      | 1.5  | V          |

| Input Voltage       |          |            |        |         |        |      |          |          |      | 1 <b>°</b> |

| (High Level)        | VIL      | 0.5,4.5    | —      | 5       | _      | -    | 3.5      | l —      | l —  |            |

| Input Leakage Curre | ent      |            | Any    |         |        |      |          |          |      |            |

|                     | IIN      | 0.5,4.5    | Input  | 5       | _      | _    | _        | _        | ±1   |            |

| 3-State Output Leak | age      |            |        |         | 1      |      |          | <b> </b> |      | μΑ         |

| Current             | IOUT     | _          | 0,5    | 5       | _      | _    | _        | ±1       | ± 5  |            |

| Input Capacitance   | CIN      |            | A      | ny Inpu | it     | •    | _        | 5        | 7.5  |            |

| Output Capacitance  |          |            |        |         |        |      | †        |          | рF   |            |

|                     | COUT     | Any Output |        |         |        |      | _        | 5        | 7.5  |            |

<sup>\*</sup>Typical values are for  $T_A = 25$  °C.

# RECOMMENDED OPERATING CONDITIONS at $T_A = Full\ Package-Temperature\ Range$

For maximum reliability, operating conditions should be selected so that operation is always within the following ranges:

| CHARACTERISTIC                                                 | LIMITS     | UNITS |

|----------------------------------------------------------------|------------|-------|

| Read Operation:                                                |            |       |

| Supply Voltage Range VCC, VDD, VSAT                            | 4 to 6.5   | \ \ \ |

| Input Voltage Range                                            | Vss to Vcc |       |

| Program Operation:                                             |            |       |

| Supply Voltage Range VCC                                       | 4 to 6.5   |       |

| Supply Voltage Range VDD, VSAT                                 | 18 to 22   | V     |

| Input Voltage Range                                            | Vss to Vcc |       |

| Input Signal Rise Or Fall Times t <sub>f</sub> ,t <sub>f</sub> | ≤ 5        | μS    |

|                                                                | 1          | 1     |

# DYNAMIC ELECTRICAL CHARACTERISTICS at TA = 25 °C; VCC, VDD, VSAT $\pm$ 5%; Input $t_f, t_f$ = 10 ns, CL = 50 pF, RL = 200 $k\Omega$

| VCC, VDD, VSAI ± 5 /6, II |                 | NDITIO | NS              | TYPICAL     |        |       |

|---------------------------|-----------------|--------|-----------------|-------------|--------|-------|

| CHARACTERISTIC            |                 |        | V <sub>DD</sub> | VSAT<br>(V) | VALUES | UNITS |

| Read Operation            |                 |        |                 |             |        |       |

| Read Cycle Time           | tRC             |        |                 |             | 1000   | ns    |

| Access Time From          |                 |        |                 |             |        |       |

| Address Change            | tM              | 5      | 5               | 5           | 1000   | ns    |

| Access Time From          |                 |        |                 |             |        |       |

| Chip Select               | tACS            | 5      | 5               | 5           | 1000   | ns    |

| Address Setup Time        | tAS             | 5      | 5               | 5           | 0      | ns    |

| Address Hold Time         | t <sub>AH</sub> | 5      | 5               | 5           | 0      | ns    |

| Bus Contention Delay      | tD              | 5      | 5               | 5           | 50     | ns    |

| Output Hold Time From     |                 |        |                 |             |        |       |

| Address Change            | tOHA            | 5      | 5               | 5           | 50     | ns    |

| Output 3-State From       |                 |        |                 |             |        |       |

| Deselection               | toTD_           | 5      | 5               | 5           | 50     | ns    |

| Access Time From          |                 |        | 1               |             |        |       |

| PGM                       | tAP             | 5      | 5               | 5           | 1000   | ns    |

| Program Operation         |                 |        |                 |             |        |       |

| Program Cycle Time        | tPC             | 5      | 18              | 18          | 10     | ms    |

| Program Cycle Time        |                 | 5      | 22              | 22_         | 0.1    | 1113  |

| Address Setup Time        | tAS             | 5      | 18,22           | 18,22       | 0      | ns    |

| Address Hold Time         | <sup>t</sup> AH | 5      | 18,22           | 18,22       | 0      | ns    |

| PGM To Outputs Inactive   | tpx             | 5      | 18,22           | 18,22       | 200    | ns    |

| Chip Select To Program    |                 | ì      |                 |             |        |       |

| Setup Time                | tcs             | 5      | 18,22           | 18,22       | 500    | ns    |

| Chip Select To Program    |                 | -      |                 |             |        |       |

| Hold Time                 | tCH             | 5      | 18,22           | 18,22       | 200    | ns    |

| PGM To Program Voltage    |                 |        |                 |             |        |       |

| Setup Time                | tps             | 5      | 18,22           | 18,22       | 500    | ns    |

| PGM To Program Voltage    |                 |        |                 |             | -      |       |

| Hold Time                 | tpH             | 5      | 18,22           | 18,22       | 200    | ns    |

| Data Setup Time           | tDS             | 5      | 18,22           | 18,22       | 200    | ns    |

| Data Hold Time            | <sup>t</sup> DH | 5      | 18,22           | 18,22       | 200    | ns    |

| Program Voltage           | tpvw            | 5      | 18              | 18          | 10     | ms    |

| Pulse Width               | PVW             | 5      | 22              | 22          | 0.1    |       |

| Program Voltage           |                 |        |                 |             |        |       |

| Rise Or Fall Time         | tpR,tpF         | 5      | 18,22           | 18,22       | 2      | μS    |

#### TABLE L. OPERATING MODES FOR CDP18U42CD

| TABLE I - OPERATING MODES FOR CDP18U42CD |                 |                 |                       |             |            |            |            |            |                 |

|------------------------------------------|-----------------|-----------------|-----------------------|-------------|------------|------------|------------|------------|-----------------|

| OPERATING MODE                           | V <sub>SS</sub> | V <sub>CC</sub> | V <sub>DD</sub><br>(V | VSAT<br>(V) | CS1<br>(V) | CS2<br>(V) | CS3<br>(V) | PGM<br>(V) | BUS 0-<br>BUS 7 |

| READ                                     | 0               | 5               | VCC                   | Vcc         | VSS        | VCC        | Vss        | ٧cc        | OUTPUT          |

| PROGRAM                                  | 0               | 5               | ال <sup>3</sup>       | 18-22       | VSS        | vcc        | ٧ss        | Vss        | INPUT           |

| DESELECT                                 | 0               | 5               | Vcc                   | Vcc         | ×          | х          | Vcc        | Vcc        | 3-STATE         |

| DESELECT                                 | 0               | 5               | Vcc                   | VCC         | Х          | ٧ss        | Х          | Vcc        | 3-STATE         |

| DESELECT                                 | 0               | 5               | Vcc                   | Vcc         | Vcc        | Х          | Х          | Vcc        | 3-STATE         |

X = DON'T CARE

Fig. 3 — Program timing diagram.

Fig. 4 — READ timing diagram.

TABLE II - POWER DISSIPATION FOR CDP18U42CD

|                         | CO                     | NDITIONS               | TYPICAL     |         |         |

|-------------------------|------------------------|------------------------|-------------|---------|---------|

| OPERATION               | V <sub>CC</sub><br>(V) | V <sub>DD</sub><br>(V) | VSAT<br>(V) | VALUES* | UNITS   |

| READ QUIESCENT          | 5                      | 5                      | 5           | 0.05    | mW      |

| READ UNSELECTED (1 MHz) | 5                      | 5                      | 5           | 10      | mW      |

| READ SELECTED (1 MHz)   | 5                      | 5                      | 5           | 20      | mW      |

| WRITE ALL 0'S           | 5                      | 18                     | 18          | 0.1     | mW      |

| While ALL 03            | 5                      | 22                     | 22          | 0.2     | 111100  |

| WRITE ALL 1'S           | 5                      | 18                     | 18          | 120     | mW      |

| While ALL 13            | 5                      | 22                     | 22          | 300     | i iiivv |

<sup>\*</sup>Typical values are for  $T_A = 25$  °C.

## **OPERATING AND HANDLING** CONSIDERATIONS

#### 1. Handling

All inputs and outputs of RCA COS/MOS devices have a network for electrostatic protection during handling. Recommended handling practices for COS/MOS devices are described in ICAN-6525 "Guide to Better Handling and Operation of CMOS Integrated Circuits.

# 2. Operating

Operating Voltage

During operation near the maximum supply voltage limit, care should be taken to avoid or suppress power supply turn-on and turn-off transients, power supply ripple, or ground noise; any of these conditions must not cause VDD-VSS to exceed the absolute maximum rating.

#### Input Signals

To prevent damage to the input protection circuit, input signals should never be greater than VDD nor less than VSS. Input currents must not exceed 10 mA even when the power supply is off.

# **Unused Inputs**

A connection must be provided at every input terminal. All unused input terminals must be connected to either VDD or VSS, whichever is appropriate.

### **Output Short Circuits**

Shorting of outputs to VDD or VSS may damage COS/MOS devices by exceeding the maximum device dissipation.

### **DIMENSIONAL OUTLINE**

# (D) SUFFIX

24-Lead Dual-In-Line Side-Brazed Ceramic Package (With Transparent Window)

| SYMBOL   | INC       | HES   | NOTE  | MILLIMETERS |       |  |

|----------|-----------|-------|-------|-------------|-------|--|

| STIVIBUL | MIN.      | MAX.  | INOTE | MIN.        | MAX.  |  |

| А        | 1.180     | 1.220 |       | 29.98       | 30.98 |  |

| С        | 0.115     | 0.175 |       | 2.93        | 4.44  |  |

| D        | 0.015     | 0.023 |       | 0.39        | 0.58  |  |

| F        | 0.04      | REF.  |       | 1.02        | REF.  |  |

| G        | 0.100 BSC |       | 1     | 2.54 BSC    |       |  |

| н        | 0.030     | 0.070 |       | 0.77        | 1.77  |  |

| j        | 0.008     | 0.012 | 3     | 0.21        | 0.30  |  |

| К        | 0.125     | 0.175 |       | 3.18        | 4.44  |  |

| L        | 0.580     | 0.620 | 2     | 14.74       | 15.74 |  |

| M        | -         | - 7   |       | -           | 7     |  |

| Р        | 0.025     | 0.050 | Ī     | 0.64        | 1.27  |  |

| N        | :         | 24    |       | - 2         | 24    |  |

NOTES:

92CM-32216

- 1. Leads within 0.005" (0.13 mm) radius of True Position at maximum material condition.

- 2. Center to center of leads when formed parallel.

- 3. When this device is supplied solder dipped, the maximum lead thickness (narrow portion) will not exceed 0.013"

When incorporating RCA Solid State Devices in equipment, it is recommended that the designer refer to "Operating Considerations for RCA Solid State Devices", Form No. 1CE-402, available on request from RCA Solid State Division, Box 3200, Somerville, N. J. 08876.

MAY 2 5 1993

025772 V R